Introduction

The project involves designing, building, and testing a Turing Complete 16-bit RISC machine using System Verilog on an FPGA board. Key softwares used include Quartus and Questa/ModelSim.

Project Features

- RISC Processor Design: Implements a simple RISC processor architecture.

- SystemVerilog Implementation: Written in SystemVerilog hardware description language.

- Simulation and Testing: Includes testbenches for thorough verification of the processor via Questa/ModelSim.

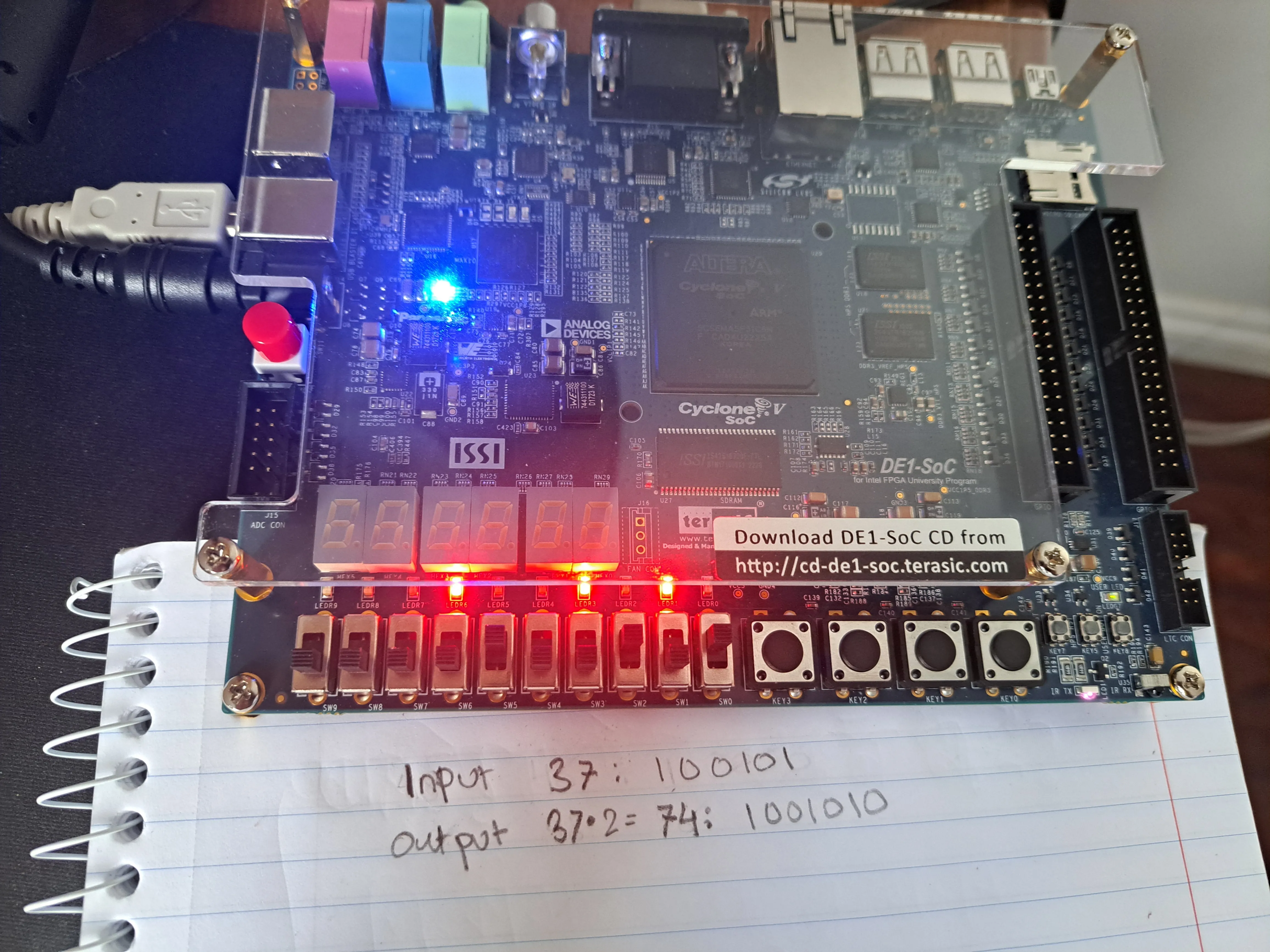

- FPGA Deployment: Configured to run on an FPGA development board (DE1-Soc).

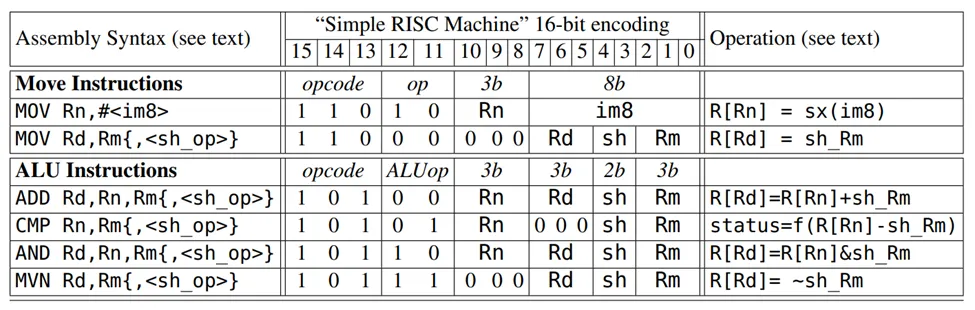

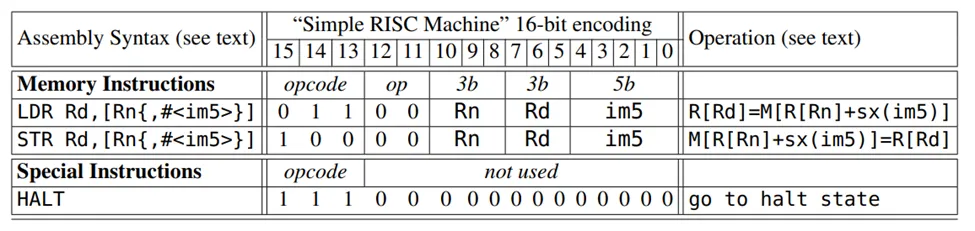

Supported Instructions

The processor can execute a variety of ARM instructions. The following diagram illustrates the ARM instruction encodings that the machine can run:

Hardware Components

- FPGA Board: DE1-SoC development board

- Processor Design: Custom RISC processor implemented in SystemVerilog

- Memory: On-chip memory for instruction and data storage

Software Description

SystemVerilog Code

Utilizing modularization, the processor is designed in SystemVerilog and includes several modules for different components of the processor. The main design files are:

RISC_top.sv: Top-level module for the RISC processorcpu.sv: Central Processing Unit moduledatapath.sv: Datapath modulealu.sv: Arithmetic Logic Unit moduleinstruction_decoder.sv: Instruction Decoder modulefinite_state_machine.sv: Finite State Machine moduleregfile.sv: Register File moduleshifter.sv: Shifter module

Testbenches

cpu_tb.sv: Testbench for the CPUdatapath_tb.sv: Testbench for the datapathRISC_top_tb.sv: Testbench for the top-level moduleRISC_check.sv: Verification module

Project Demonstration

- A video demonstration of the RISC processor in action voiced by my partner Afeef can be found linked here: https://youtu.be/biTuX5kdb8c

Future Improvements

- Enhance the processor design to support more complex instructions.

- Implement pipelining for improved performance.

- Expand the testbench coverage to include more edge cases and scenarios.